# A Three-Phase Symmetrical DC-Link Multilevel Inverter with Reduced Number of DC Sources

Md Mubashwar Hasan, *Student Member, IEEE*, A. Abu-Siada, , *Senior Member, IEEE*, and Mohamed S. A. Dahidah, *Senior Member, IEEE*

Abstract— This paper presents a novel three-phase DC-link multilevel inverter topology with reduced number of input DC power supplies. The proposed inverter consists of series-connected half-bridge modules to generate the multilevel waveform and a simple H-bridge module, acting as a polarity generator. The inverter output voltage is transferred to the load through a threephase transformer, which facilitates a galvanic isolation between the inverter and the load. The proposed topology features many advantages when compared with the conventional multilevel inverters proposed in the literatures. These features include scalability, simple control, reduced number of DC voltage sources and less devices count. A simple sinusoidal pulse-width modulation technique is employed to control the proposed inverter. The performance of the inverter is evaluated under different loading conditions and a comparison with some existing topologies is also presented. The feasibility and effectiveness of the proposed inverter are confirmed through simulation and experimental studies using a scaled down low-voltage laboratory prototype.

*Index Terms*— Hybrid multilevel inverter; DC-link inverter; half-bridge module; symmetric DC voltage supply.

### I. INTRODUCTION

MULTILEVEL inverters have received great attention from both academia and industry in the past few decades due to their distinctive features compared to their conventional two-level counterparts [1, 2]. These include, lower switching losses and stress on the semiconductor devices, high quality output waveforms, reduced electromagnetic interference and smaller filtering requirements [3-6]. Cascaded Multilevel Inverters (CMLI) have received special preference in various industrial applications, especially, renewable integration [5, 7, 8]. This is particularly because of their modularity and redundancy features along with the absence of complicated capacitor voltage balancing issue, which is a common problem with other topologies such as diode and capacitor clamped inverters [9-11]. Several variations of CMLI circuit topology have been documented in the open literature, aiming to increase the attained voltage levels, which ultimately

Manuscript received May 12, 2017; revised September 15, 2017 and November 15, 2017; accepted November 29, 2017. The authors would like to acknowledge the contribution of an Australian Government Research Training Program Scholarship in supporting this research.

Md Mubashwar Hasan and A. Abu-Siada are with Department of Electrical and Computer Engineering, Curtin University, Perth, Australia (m.hasan12@postgrad.curtin.edu.au, a.abusiada@curtin.edu.au)

M. S. A. Dahidah is with School of Engineering, Newcastle University, Newcastle Upon Tyne NE1 7RU, U.K. (mohamed.dahidah@ncl.ac.uk).

improve the quality of the output waveform [12]. Hybrid (or else known as asymmetric) cascaded multilevel inverter is one of the proposed variations, where different input voltage levels are usually considered [13-16]. Reduced device count can be achieved with hybrid CMLIs, however lack of modularity and unequal voltage distribution on the power switches makes them unattractive for utility-grade applications. On the other hand, another major challenge with CMLIs is the need for independent isolated DC power supplies, which impose additional restrictions and complexity, especially when higher number of levels in the output voltage waveform is required. Several attempts have been reported in the open literature aimed to reduce the required number of the DC power supplies [11, 17-19].

For instance, [19-21] proposed a new CMLI comprising half-bridge cells to synthesize the unipolar staircase-shape waveform and a full-bridge inverter as a polarity generator. This has considerably reduced the devices count and the required number of DC power supplies compared with conventional multilevel inverters. Some balancing capacitors are utilized within the half-bridge modules to reduce the number of rectifiers in [19]. However as mentioned in [11], balancing these capacitors requires a complicated control scheme. An extension of the topology proposed in [20, 21] was recently reported in [11], where a further reduction in the required DC power supplies was achieved, however a possible extension to three-phase system was not reported.

A modular three-phase half-bridge based CMLI is proposed in [22-24]. However, these topologies require a higher number of isolated DC-supplies, which increases the cost and complexity as well as the requirement for a complicated modulation technique. Hybrid three-phase CMLI is reported in [17, 18], where the cascaded half-bridge cells are connected with a three-phase voltage source inverter. This has significantly reduced the number of the semiconductor devices as well as the required DC supplies. However, the need for isolated DC power supplies could not be avoided.

Another variation of the topologies studied in [11] was proposed in [25, 26], where only a single DC power supply is used and the other levels of the output waveform were realized through floating capacitors. However, it is evident that this topology is highly load-dependent and requires sophisticated capacitor voltage balancing algorithms, especially if high number of output voltage levels is considered.

Multi-winding transformers are utilized in [27, 28] to maximize the output voltage levels. The inverter uses only a single DC power supply and the secondary windings of the single-phase transformers are cascaded to form the multilevel output voltages, where the number of levels is a function of the transformers' turns ratios. Although this has helped to reduce the required DC power supplies, the large number of single-phase transformers makes it impractical and not attractive as the size and complexity increases with each additional level in the output voltage [11].

In overall, the above discussion reveals that efforts have been made on CMLI to either reduce the device-count or DC power supplies or both. While the reduction of DC power supplies was achievable for single-phase CMLI [11], it becomes at least three times when extended to three-phase version [17-20, 22].

Therefore, this paper proposes a new symmetric three-phase CMLI based on half-bridge cells with reduced number of DC power supplies. This topology can be considered as an extension and upgrade version of the three-phase topology proposed in [19, 20]. However, nearly 30% more voltage levels in the line voltages can be achieved by utilizing the same number of semiconductor devices. Furthermore, the proposed topology reduces nearly 67% of the rectifiers required as input DC supplies for the symmetric half-bridge modules.

The rest of the paper is organized as follows: Section II presents the operation principle of the proposed symmetric CMLI along with its modulation technique. Section III presents and discusses selected simulation and experimentally validated results. Comparison between the proposed topology and conventional CMLI is drawn in Section IV. Finally, the work is concluded in Section V.

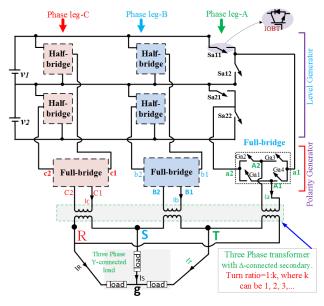

Fig. 1 The proposed three-phase CMLI with two half-bridge cells per phase leg

## II. THE PROPOSED MULTILEVEL INVERTER AND ITS MODULATION STRATEGY

Figure 1 illustrates the proposed CMLI, which consists of two stages. The first stage is a level generator, which generates the unipolar multilevel voltage waveforms by utilizing the cascaded half-bride modules. As shown in Fig. 1, each three half-bridge modules in the three-phase legs-A, B and C are fed from a non-isolated DC power supply. In reality, the DC-power supplies can be battery sources, or rectifier output terminals. Furthermore, the DC supplies can be equally obtained from photovoltaic (PV) output terminals or other renewable energy source. To realize constant output power and voltage for renewable energy sources of intermittent characteristics, some control algorithms such as constant voltage source mode can be employed [29]. It is worth noting that the half-bridge modules will have the same blocking voltage requirement since they are connected across the same DC-supply. This ensures modularity and simple control methods. The second stage is the polarity generator, which utilizes a simple full-bridge inverter to bipolarize the multilevel output voltage waveforms produced by the first stage.

A three-phase transformer couples the outputs of the polarity generator with the load, providing a galvanic isolation as well as boosting to the output voltage. It should be noted that although in Fig. 1 the transformer secondary windings are connected in  $\Delta$ , it could be also connected in Y, if required. Furthermore, the CMLI presented in Fig. 1 can be easily expanded to generate higher number of levels in the output voltage waveform by adding more half-bridge modules into the level generator. The number of levels, m in the output voltage of each polarity generator by utilizing n-number of half-bridge modules in each phase leg is given by:

$$m=2n+1 \tag{1}$$

Considering equal input DC voltages  $(v_1, v_2, ..., v_n)$  to the *n*-number of the half-bridge modules in the level generator stage, the input DC voltages can be written as,

$$v_1 = v_2, \dots = v_n = V_{DC};$$

(2)

where  $V_{DC}$  represents a constant value

While the half-bridge modules in the level generator utilize low voltage, high switching frequency devices, the low frequency switches used in the full-bridge modules in the polarity generator experience a voltage stress of a magnitude equals to the summation of the input DC voltage sources [20]. Hence, the voltage stress or standing voltage,  $V_{\rm pg,\ stress}$  on the polarity generator switches can be expressed as,

$$V_{pg, stress} = nV_{DC}$$

(3)

It is to be noted that because they are operating at the fundamental switching frequency of 50 Hz, full-bridge modules do not exhibit significant switching losses. On the other side, state-of-the-art technology currently offers switching devices such as Insulated Gate Bipolar Transistors (IGBT)-module, FZ500R65KE3 that can withstand a collector to emitter voltage up to 6.5 kV [30]. Moreover, the operating voltage capacity of the switching devices can be extended by connecting multiple switches in series. A number of CMLIs topologies utilizing half-bridge and H-bridge modules have been implemented for

high voltage applications and can be found in the literatures [19, 31]. The rating of the switching devices in the proposed CMLI can be identified according to the voltage requirement of the intended application. It is worth mentioning that as the three-phase transformer is an essential component in the proposed topology, it will inherently fulfill the galvanic isolation requirement for renewable energy grid-connected applications [31].

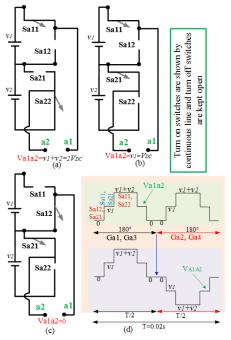

Fig. 2 Switching logics for generating different levels in the level generator output voltages: (a) logic for generating  $2V_{DC}$ , (b) logic for generating  $V_{DC}$ , (c) logic for generating 0, (d) desired output in the level generator and polarity generator output voltage

Figures 2(a)-(c) show the different switching states of the level generator, producing different output voltage levels ( $v_1+v_2$ ,  $v_1$ , 0). Figure 2 (d) illustrates the generated AC output voltage in the polarity generator at phase leg-A, where the polarity generator flips the waveform in every 180°.

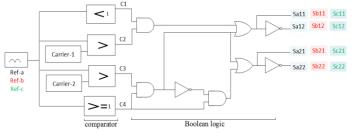

The main focus of this paper is to develop a new inverter topology. Conventional Sinusoidal Pulse-Width Modulation (SPWM) technique is a well-known and easy to implement technique [32]. Hence, SPWM is adopted to demonstrate the effectiveness of the proposed topology. As shown in Fig. 3, the reference signals, Ref-a, Ref-b, Ref-c are the rectified sinusoidal waveforms with a 120<sup>0</sup> phase shift from each other. These are then compared with two carrier signals (carrier-1 and carrier-2) to generate the required gating signals. Same switching signals generation logic is utilized for each phase leg.

### III. SEMICONDUCTOR LOSSES AND CONVERTER EFFICIENCY

The semiconductor losses are considered as a crucial design and selection criterion for any converter circuit as they influence and define the required thermal management, which contributes to the estimation of the overall cost/volume/weight of the inverter. There are two dominant losses in the semiconductor devices; the static and the dynamic losses. The on-state resistance and the forward voltage drop of the

semiconductor devices are responsible for the conduction losses, while the dynamic losses are produced during the turn on/off actions dictated by the switching frequency of the device.

The instantaneous conduction losses of a transistor  $(\sigma_{c,T})$  and a diode  $(\sigma_{c,D})$  at any instant of time (t) can be expressed as,

$$\sigma_{c,T}(t) = [V_T + R_T i^{\beta}(t)]i(t)$$

$$\sigma_{c,D}(t) = [V_D + R_D i(t)]i(t)$$

(4)

where, the on-state voltage drops of the transistor and diode are expressed by  $V_T$  and  $V_D$ , respectively. The on-state resistances of the transistor and diode, are given by  $R_T$  and  $R_D$ , respectively.  $\beta$  and i(t) are the transistor amplification factor and a transistor or diode current at any instant of time, respectively.

Hence, the average conduction losses in both, the transistor and the diode, denoted by  $P_{c,T}(t)$  and  $P_{c,D}(t)$ , respectively are given by:

$$P_{c,T}(t) = \frac{1}{2\pi} \int_0^{2\pi} [\{V_T + R_T i^{\beta}(t)\} i(t)] d(\omega t)$$

$$P_{c,D}(t) = \frac{1}{2\pi} \int_0^{2\pi} [\{V_D + R_D i(t)\} i(t)] d(\omega t)$$

(5)

The total average conduction losses can then be calculated from,

$$P_{c}(t) = \int_{0}^{2\pi} [\{N_{Transistor}(t) * P_{c,T}(t)\} + \{N_{Diode}(t) * P_{c,D}(t)\}] d(\omega t)$$

(6)

where  $N_{Transistor}$  and  $N_{Diode}$  are the number of transistors and diodes, respectively, in the same current path at any instant of time.

Fig. 3 Block diagram of the modulation technique

Similarly, the total switching power losses of the semiconductor devices are calculated by the energy losses during turn-on ( $t_{on}$ ) and turn-off ( $t_{off}$ ) periods. The switching energy losses during turn-on ( $E_{on}$ ) and turn-off ( $E_{off}$ ) can be derived from,

$$E_{on} = \int_{0}^{t_{on}} v(t)i(t)dt$$

$$= \int_{0}^{t_{on}} \left[ \left( \frac{V_{sw}}{t_{on}} * t \right) \left( -\frac{I}{t_{on}} \right) * (t - t_{on}) \right] dt$$

$$= \frac{1}{6} V_{sw} * I * t_{on}$$

$$E_{off} = \int_{0}^{t_{off}} v(t)i(t)dt$$

$$= \int_{0}^{t_{off}} \left[ \left( \frac{V_{sw}}{t_{off}} * t \right) \left( -\frac{I'}{t_{off}} \right) * (t - t_{off}) \right] dt$$

$$= \frac{1}{6} V_{sw} * I' * t_{off}$$

$$(7)$$

where  $V_{sw}$  and I, represent the off-state voltage and current of

the device, respectively. I' represents the device current measured just before the device is turned off.

The total switching power losses ( $P_{sw}$ ), for a time-period T can be calculated from,

$$P_{sw} = \frac{1}{T} \left[ \sum_{1}^{N_{switch}} \left\{ (N_{on} * E_{on}) + (N_{off} * E_{off}) \right\} \right]$$

(8)

where the number of turn-on and off counts of a switch in a cycle is given by  $N_{on}$  and  $N_{off}$ ; respectively.

The overall semiconductor losses of the proposed CMLI can be estimated by the total conduction and switching losses of all used semiconductors, expressed as:

$$P_{total\_loss} = P_c(t) + P_{sw} \tag{9}$$

If the output power is  $P_{out}$ , the inverter efficiency  $(\eta)$  can be calculated from:

$$\eta\% = \left(\frac{P_{out}}{P_{total\ loss} + P_{out}}\right) * 100\% \tag{10}$$

where the output power is calculated from:

$$P_{out} = \sqrt{3} * \frac{3V_{dc}}{\sqrt{2}} * \frac{I_{line}}{\sqrt{2}} * PF$$

(11)

If the power factor (PF) of the connected load is nearly 0.8 lagging, when connecting a load of  $20+j15.7\Omega$  in each phase leg, using (10), the output power is 98.64 watts, which gives an overall efficiency of about 97%.

### TABLE I PROPERTIES SYSTEM SPECIFICATIONS OF THE PROPOSED INVERTER

| TROI ERTIES STSTEM STECHTCATIONS OF THE TROI OSED INVERTER |              |  |  |  |

|------------------------------------------------------------|--------------|--|--|--|

| Input DC sources $(v_1, v_2)$                              | 60V each     |  |  |  |

| Carrier frequency                                          | 4 kHz        |  |  |  |

| Switching controller                                       | TMS320F2812  |  |  |  |

| Ratings of IGBT                                            | HGTG20N60B3D |  |  |  |

| Magnitudes of the line voltages                            | 270V (peak)  |  |  |  |

| Number of levels in line voltages                          | 13           |  |  |  |

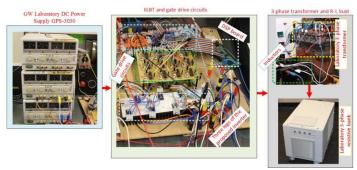

Fig. 4 Experimental test-rig setup

### IV. SIMULATION AND EXPERIMENTAL RESULTS

Fig. 4 illustrates the experimental test-rig of the proposed inverter, developed at the Green Electric Energy Park (GEEP), Curtin University [33]. On the other hand, simulation analysis is carried out using the Matlab/Simulink software package. The main parameters of the inverter prototype are summarized in Table 1. The input DC voltages from the 'GW Laboratory DC

power supplies GPS-3030' are set to provide a constant DC voltage of 60V, i.e. ( $v_1$ = $v_2$ =60 volts). Both, the level generator and polarity generator stages require twelve IGBTs, each. A digital signal processor (DSP), TMS320F2812 is used to generate the real time switching gate signals. The gate signals from the DSP are connected to the IGBT gates through 24-gate drive circuits. The role of gate drive circuits is to isolate the common ground of the DSP output gate pulses and boost-up their magnitudes to nearly 15 volts. As shown in Fig. 4, there are two printed circuit boards comprising 24-gate drive circuits for the 24 IGBTs in the level generator and polarity generator stages.

In this paper, the conventional SPWM modulation strategy is considered with a carrier frequency of 4kHz for both, simulation and experimental studies. The modulation index  $M_i$  is expressed as [32].

$$M_i = \frac{A_m}{(N_p - 1)A_c} \tag{12}$$

where  $A_m$  is the magnitude of the reference sine waveform and  $A_C$  is the magnitude of the carrier signal. Modulation index,  $M_i$  has an influence on the magnitude of the output line voltages and line currents [32]. The output of the polarity generator is connected to the primary of a three-phase isolation transformer with a turn ratio of 1:1, as shown in Fig. 4.

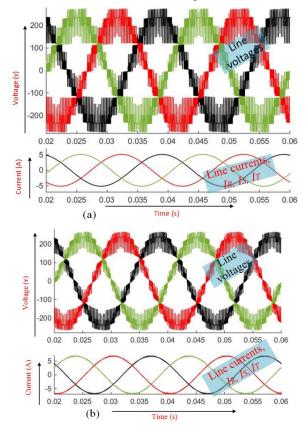

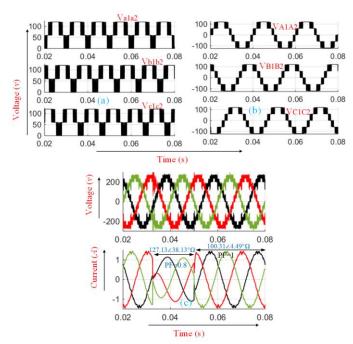

Fig. 5 Simulation results of the output line voltages and line currents for (a) load of nearly 0.8–lagging power factor and (b) load of nearly unity power factor

As previously mentioned, the secondary side of the transformer can be connected in either  $\Delta$  or Y. The output line voltages can therefore be presented by (13) or (14) for  $\Delta$  or Y connection, respectively.

$$\begin{bmatrix} V_{RS} \\ V_{ST} \\ V_{TS} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} V_{C1C2} \\ V_{B1B2} \\ V_{A1A2} \end{bmatrix}$$

(13)

The performance of the proposed inverter under various loading conditions is assessed as elaborated in the following case studies.

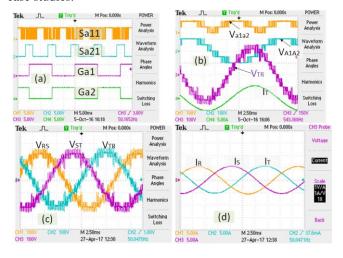

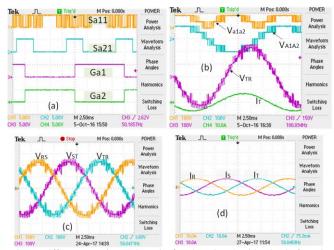

Fig. 6 Different experimental results for phase leg-A with a load of nearly 0.8 lagging power factor: (a) gate pulses in half-bridge and full bridge module at phase leg-A, (b) level and polarity generator output voltages along with the line voltage and line current for phase leg-A, (c) three phase line voltages and (d) three phase line currents.

### A. Case study 1: The impact of load power factor

Fig. 5 shows the simulation results of the line voltage and line current waveforms of the proposed inverter under load power factor of nearly 0.8 (lagging) and unity power factor, when each phase leg is connected with balanced inductive loads of  $(20+j15.7\Omega)$  and  $(20+j1.57\Omega)$ , respectively.

Fig. 7 Different experimental results for phase leg-A with a load of nearly unity power factor: (a) gate pulses in half-bridge and full bridge module at phase leg-A, (b) level and polarity generator output voltages along with the line voltage and line current for phase leg-A, (c) three phase line voltages and (d) three phase line currents.

On the other hand, Figs. 6 and 7 illustrate different experimental results for nearly 0.8 lagging and unity power factor loads, respectively. Tektronix TPS2014B digital storage oscilloscope is utilized for capturing the experimental waveforms and displaying their harmonic spectrums. It is worth mentioning that, no harmonic filters were utilized while taking the results. Figs. 6(a) and 7(a) illustrate the experimental gating signals for both, the level generator and polarity generator switches,  $S_{a11}$ ,  $S_{a21}$ ,  $G_{a1}$ ,  $G_{a2}$  in phase leg-A. The corresponding level generator output voltage ( $V_{a1a2}$ ), the polarity generator output voltage ( $V_{A1A2}$ ), line voltage ( $V_{TR}$ ) and line current ( $I_T$ ) are shown in Figs. 6(b) and 7(b). Moreover, Figs. 6(c), 6(d) and 7(c), 7(d) show the three-phase line voltages and line currents, respectively.

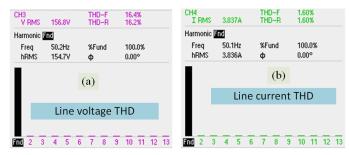

Fig. 8 THD results for nearly 0.8 lagging PF load: (a) THD for line voltage waveform, (b) THD for line current waveform

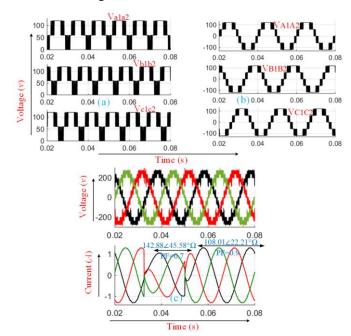

The total harmonic distortions (THD) of the line voltage and line current waveforms of the two cases above are shown in Figs. 8 and 9, respectively. It can be observed that the change of the load PF from 0.8 lagging to unity does not influence the number of levels in the line voltage waveforms. However, the THD in the line voltage and line current waveforms is changed due to the change in the load PF.

Fig. 9 THD results for nearly unity PF load: (a) THD for line voltage waveform, (b) THD for line current waveform

It is worth mentioning that the inductance of an inductive load acts as a line current harmonic filter [34], consequently, the line current comprises less harmonics in the case of 0.8 lagging PF load as opposed to unity PF load. The THD of the line current waveforms is less than 5% in both loading conditions, which satisfies the IEEE standard [35]. On the other hand, the value of voltage THD is less than the cascaded MLI proposed in [18-20, 22]. The line voltage THD can be kept within acceptable limit, if a small filter is connected at the output terminals or through increasing the number of levels in the line voltages by cascading more half-bridge cells in each phase leg.

Fig. 10 Simulation results for a dynamic change in the load from nearly unity PF  $(100.31 \angle 4.49^{\circ}\Omega)$  to 0.8 lagging PF  $(127.13 \angle 38.13^{\circ}\Omega)$ : (a) level generator output voltage, (b) polarity generator output voltage (phase voltage) and (c) line voltage and line current

## B. Case study 2: The performance of inverter under load dynamics

Inverter output voltage and current waveforms are observed during load dynamic conditions. Fig. 10 shows the simulation results when a load of nearly unity power factor  $(100+j7.85\Omega)$  per phase leg) changed at t=0.0325s to  $100+j78.5\Omega$  per phase leg. It is assumed that this change lasts for a duration of 0.0175s after which the original load is retained.

Fig. 11 Simulation results for a dynamic change in the load from nearly 0.9 lagging PF  $(108.01 \angle 22.21^{\circ}\Omega)$  to 0.7 lagging PF  $(142.88 \angle 45.58^{\circ}\Omega)$ : (a) level generator output voltage, (b) polarity generator output voltage (phase voltage) and (c) line voltage and line current

Although a little distortion can be observed in the line voltage waveforms in Fig. 10(c) during the transition period, no effect is found on the level generator output voltages shown in Figs. 10(a) and 10(b). Similar observation can be seen in Fig. 11 when a load of  $100+j40.82\Omega$  per phase leg changes to  $100+j102.05\Omega$  per phase leg at t=0.0325s for a duration of 0.0175s.

Fig. 12 Simulation results for a dynamic change in the load magnitude with the same PF: (a) Line voltage, (b) Line current

The performance of the proposed CMLI is also investigated with a change in the load magnitude with the same power factor. Fig. 12 shows the inverter line voltage and line current waveforms when the load is doubled (i.e. 40 +j31.42  $\Omega$  /phase leg to 80+j62.84  $\Omega$  /phase leg) at t=0.0325s for a duration of 0.0175s. Same observations in the above two cases can be noticed in this case study as well.

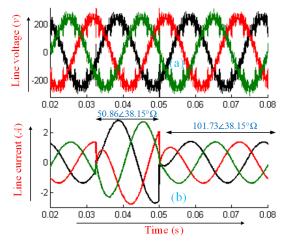

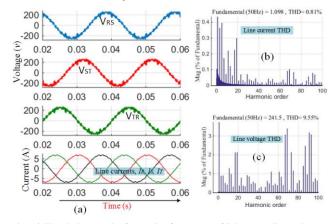

Fig. 13 Simulation results for carrier frequency of 8 kHz: (a) line voltages and currents, (b) line current THD, (c) line voltage THD

## C. Case study 3: Impact of changing the carrier frequency on the inverter performance

To assess the performance of the proposed inverter with high carrier frequency, the carrier frequency is increased from 4 kHz to 8 kHz. Fig. 13 shows the inverter's output line voltages and line currents at 8 kHz carrier frequency and a load of 20+j15.7 $\Omega$ /phase leg. In this case, the THD of the line voltage and line current waveforms is reduced from 15.6% and 1.37% in case of 4 kHz carrier frequency to 9.55% and 0.81%; respectively in

case of 8 kHz carrier frequency.

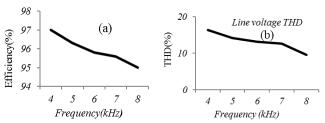

Fig. 14 Effect of carrier frequency on (a) Semiconductor efficiency, (b) Line voltage THD

The efficiency of the proposed inverter and the quality of the line voltage waveforms are evaluated in a wide range of carrier frequencies. Figs. 14(a) and 14(b) show the THD of the line voltage waveforms and inverter semiconductor efficiency for a set of carrier frequencies. While the quality of the line voltage waveforms is found better for higher carrier frequencies, semiconductor efficiency degrades with higher frequencies due to increased switching losses.

$\label{eq:Table 2} Table \ 2$  Inverter performance at different modulation index (based

| ON SIMULATION RESULTS)          |       |       |      |      |      |  |

|---------------------------------|-------|-------|------|------|------|--|

| Modulation index                | 0.6   | 0.7   | 0.8  | 0.9  | 1    |  |

| Inverter efficiency (%)         | 76    | 80    | 94   | 95   | 97   |  |

| Peak line voltage (V)           | 190   | 200   | 210  | 250  | 270  |  |

| Peak line current (A)           | 3.3   | 3.54  | 3.8  | 4.6  | 5.2  |  |

| THD <sub>line voltage</sub> (%) | 38.11 | 36.92 | 34   | 23.3 | 15.6 |  |

| THD <sub>line current</sub> (%) | 3.62  | 2.51  | 2.14 | 1.53 | 1.37 |  |

A wide range of SPWM switching frequency (1 kHz to 12 kHz) has been proposed in the literature for different multilevel inverters topologies [19, 22, 36, 37]. The optimum switching frequency is a trade-off between switching losses and the quality of the output voltage and hence the size of the system. According to Fig. 14(a), to maintain the efficiency of the proposed inverter at 97% or above, a carrier frequency of 4 kHz is considered. The efficiency will be reduced to 95.8% if a carrier frequency of 6 kHz is used. On the other hand, the line voltage THD corresponding to 4 kHz carrier frequency is 15.6% while it slightly reduced to 13.14% with a carrier frequency of 6 kHz (Fig. 14(b)). Hence, for the proposed topology a carrier frequency of 4 kHz provides a satisfactory performance in terms of inverter efficiency and quality of the output waveforms. At this frequency, the THD in the line current was found to be 1.37% as per the above case studies.

### D. Case study 4: Impact of Modulation index

Table 2 shows the inverter efficiency and the magnitudes of the inverter output line voltage and line current for different modulation indexes,  $M_i$  when the inverter is loaded by  $20+j15.7\Omega$  in each phase leg and operated at a carrier frequency of 4 kHz. As can be seen from Table 2, the inverter efficiency significantly reduced when  $M_i$  is less than 0.8. Table 2 also shows that while the magnitudes of the line voltage and line current increase with the increase of the modulation index, the THD in both waveforms is decreasing.

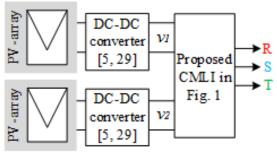

Fig. 15 Simplified block diagram for PV-application of the proposed CMLI

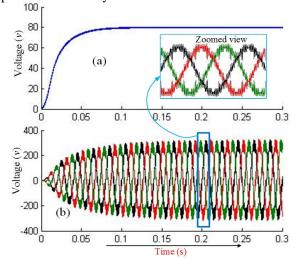

### E. Case study 5: photovoltaic application

As mentioned in section II, the input DC supplies can be obtained from photovoltaic output terminals or other renewable energy source. In this case study, the feasibility of the proposed inverter with PV system is assessed. The performance of the proposed inverter is investigated by replacing the two input DCpower supplies in Fig. 1 by two PV-modules. A block diagram of PV-array connected to the proposed CMLI in this paper is shown in Fig. 15. DC-DC converter is utilized to maintain the DC voltages  $v_1$  and  $v_2$  at constant levels as per the control approach proposed in [5, 29]. It is assumed that a constant voltage control algorithm as presented in [5, 29] is utilized to maintain the PV-modules output voltage at 80 volts as shown in Fig. 16(a). With a load of 20+j15.7 $\Omega$ , the MLI output line voltage waveforms are as shown in Fig. 16(b). The number of levels and the THD of the output line voltage waveforms remain unchanged in comparison to the output waveforms depicted in Case study 1.

Fig. 16 PV application: (a) PV module output voltage, (b) proposed inverter output line voltage

In addition to their application in PV power conversion, half-bridge module based multilevel inverters have been also utilized for medium voltage and electric vehicle applications as reported in [18, 38]. It is expected that the topology proposed in this paper can also be utilized for the aforementioned applications and provide additional advantages, e.g. galvanic isolation and reduced input DC-voltage supplies. According to manufacturers' data sheets [39], the utilized three-phase transformer is of high efficiency (up to 99%).

$TABLE \ 3$   $Comparison \ Between \ The \ Proposed \ Topology \ and \ Conventional \ mli$

|                                           | Diode clamped    | Flying Capacitor | CHB       | Proposed CMLI |

|-------------------------------------------|------------------|------------------|-----------|---------------|

| Number of clamping diodes [20]            | 3*(m-1)*(m-2)    | 0                | 0         | 0             |

| Number of clamping capacitors [20]        | 0                | 3(m-1)*(m-2)/2   | 0         | 0             |

| Number of voltage divider capacitors [20] | 3*(m-1)          | 3*( <i>m</i> -1) | 0         | 0             |

| Number of switching devices [20]          | 6*( <i>m</i> -1) | 6*(m-1)          | 6*(m-1)   | 3*(m+3)       |

| Number of DC supplies [20]                | 1                | 1                | 3(m-1)/2  | (m-1)/2       |

| Output Transformer [28]                   | 1                | 1                | 1         | 1             |

| Inverter Efficiency [40] [41] [42]        | Up to 96%        | Up to 97%        | Up to 95% | 97%           |

Hence, the overall efficiency of the proposed inverter will not be significantly affected in comparison with other existing halfbridge based CMLI. Moreover, as this topology requires less number of power electronic devices in comparison to other cascaded topologies, the overall losses are expected to be decreased.

#### V. COMPARISON WITH OTHER MLI TOPOLOGIES

#### A. Comparison with conventional topologies

Table 3 shows a general comparison between the proposed CMLI and conventional MLI i.e. diode clamped, flying capacitor and cascaded H-bridge (CHB) topologies with respect to the device count (as a function of the number of levels in the output voltage, *m*) and overall efficiency. In contrary with conventional MLI, Table 3 shows that the proposed CMLI does not require any diodes or capacitors, which is the main issue of conventional diode clamped and flying capacitor topologies [20]. The table also shows that the proposed topology requires 3(*m*+3) switching devices while other topologies require 6(*m*-1) switching devices. Hence, for any number of levels above 5, the proposed CMLI will require the least number of switching devices. Moreover, the proposed CMLI requires less number of DC-supplies than the CHB inverter.

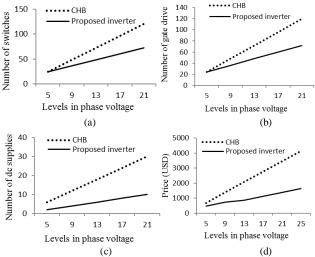

Fig. 17 Device counts and cost comparison with CHB: (a) number of switching devices, (b) number of gate drivers, (c) number of DC power supplies, (d) cost comparison per phase voltage level

Fig. 17 shows a comparison between the proposed inverter and conventional cascade H-bridge (CHB) inverter [42, 43] as a function of the number of levels m in the output voltage waveform. As shown in Fig. 17(a-c), the implementation of the

proposed inverter calls for less number of power electronic switches, gate drive circuits and DC-supplies. Fig. 17(d) shows a cost comparison between the proposed CMLI and conventional CHB-based MLI to obtain 1.5kV (peak) in the line voltage. Cost estimation includes IGBT modules, gate drivers and full-bridge rectifiers and is based on 2017 market prices [44]. It is worth mentioning that a three phase transformer is an essential part in the conventional multilevel inverters for high-power grid integration to provide the required galvanic isolation [28]. Hence, the isolation transformer in the proposed topology in this paper does not incur extra cost when the proposed cascaded inverter is utilized as a grid connected PV inverter. Fig. 17 shows that the proposed topology is a cost-effective choice when compared with the conventional CHB multilevel inverter topologies.

### B. Comparison with other half-bridge based topologies

The main emphasis of the proposed inverter aimed at maximizing the number of output voltage levels with reduced number of DC-voltage supplies by utilizing the symmetry properties. Therefore, it is essential to compare the proposed topology with other equivalent half-bridge based topologies reported in the literatures [18, 19, 22] to confirm its superiority. As summarized from Table 4, different aspects are taken into account to draw a sensible comparison, this includes: the number of half-bridge cells, total number of power electronic switching devices, gate drive circuits, number of DC-power supplies or DC-link capacitors, number of the attainable output voltage levels in the line voltages. As can be seen in Table 4, the proposed topology achieves higher number of output voltage levels by utilizing the same number of power electronic switching devices and gate drive circuits when compared with topologies proposed in [18, 19, 22].

Specifically, the topology proposed in [22], requires more than twice the number of total switching devices, gate drive circuits and DC-supplies for generating lower number of levels in the line voltage compared with the proposed topology in this paper. On the other hand, although the topology proposed in [18], requires less number of symmetric half-bridge cells, it only generates seven-levels in the output line voltage. The topology proposed in [18] would require seven symmetric half-bridge modules in each phase leg to generate 13-level at the output line voltage, which is achieved in the proposed topology in this paper by only using 3 symmetric half-bridge modules. This means, 42-switching device along with 19 DC-power supplies will be required, if the topology proposed in [18], is extended to generate 13-levels in the line voltage.

| $TABLE\ 4\ COMPARISON\ OF\ THE\ PROPOSED\ THREE-PHASE\ SYMMETRIC\ HALF-BRIDGE\ TOPOLOGY\ WITH\ OTHER\ HALF-BRIDGE\ TOPOLOGIES\ PROPOSED\ IN\ THE$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| LITERATURES                                                                                                                                       |

|                                 | Proposed topology in this paper | Three phase topology proposed in [19] | Three phase topology proposed in [22] | Three phase topology proposed in [18] |

|---------------------------------|---------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| No of half-bridge cells         | 6                               | 6                                     | 15                                    | 9                                     |

| No of total switching devices   | 24                              | 24                                    | 42                                    | 18                                    |

| No of gate driver               | 24                              | 24                                    | 42                                    | 18                                    |

| No of DC supplies or capacitors | 2                               | 6                                     | 15                                    | 9                                     |

| No levels in the line voltage   | 13                              | 9                                     | 11                                    | 7                                     |

[11]

Interestingly, the proposed cascaded multilevel inverter in this paper requires the lowest number of DC-supplies than any other topology presented in Table 4.

#### VI. CONCLUSION

This paper presents a new symmetrical multilevel inverter topology with two different stages. The proposed inverter requires less power electronic devices and features modularity, hence simple structure, less cost, and high scalability. The number of input DC-supplies for the proposed topology is found to be nearly 67% less than the similar symmetric half-bridge topologies, which is a great achievement for industrial applications. This phenomenon will reduce the complexity of DC voltage management. As being a symmetric structure, all the switching devices experience same voltage stress, which is a very important factor for high voltage applications. The feasibility of the proposed inverter is confirmed through simulation and experimental analysis for different operating conditions.

### REFERENCES

- [1] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. magazine*, vol. 2, pp. 28-39, 2008.

- [2] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, pp. 518-523, 1981.

- [3] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, et al., "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, pp. 2553-2580, 2010.

- [4] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, vol. 49, pp. 724-738, 2002.

- [5] B. Xiao, L. Hang, J. Mei, C. Riley, L. M. Tolbert, and B. Ozpineci, "Modular cascaded H-bridge multilevel PV inverter with distributed MPPT for grid-connected applications," *IEEE Trans. Ind. Appl.*, vol. 51, pp. 1722-1731, 2015.

- [6] J. Pereda and J. Dixon, "High-frequency link: a solution for using only one dc source in asymmetric cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 58, pp. 3884-3892, 2011.

- [7] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 57, pp. 2197-2206, 2010.

- [8] M. R. Islam, G. Youguang, and Z. Jianguo, "A high-frequency link multilevel cascaded medium-voltage converter for direct grid integration of renewable energy systems," *IEEE Trans. Power. Electron.*, vol. 29, pp. 4167-4182, 2014.

- [9] H. Akagi, "Classification, terminology, and application of the modular multilevel cascade converter (MMCC)," *IEEE Trans. Power. Electron.*, vol. 26, pp. 3119-3130, 2011.

- [10] N. Kawakami, S. Ota, H. Kon, S. Konno, H. Akagi, H. Kobayashi, et al., "Development of a 500-kW modular multilevel cascade converter for battery energy storage systems," *IEEE Trans. Ind.* Appl., vol. 50, pp. 3902-3910, 2014.

- E. Babaei, M. F. Kangarlu, and M. Sabahi, "Extended multilevel converters: an attempt to reduce the number of independent DC voltage sources in cascaded multilevel converters," *IET Power Electron.*, vol. 7, pp. 157-166, 2014.

- [12] N. Prabaharan and K. Palanisamy, "Comparative analysis of symmetric and asymmetric reduced switch MLI topologies using unipolar pulse width modulation strategies," *IET Power Electron.*, vol. 9, pp. 2808-2823, 2016.

- [13] E. Babaei, M. F. Kangarlu, and M. Hosseinzadeh, "Asymmetrical multilevel converter topology with reduced number of components," *IET Power Electron.*, vol. 6, pp. 1188-1196, 2013.

- [14] H. Belkamel, S. Mekhilef, A. Masaoud, and M. A. Naeim, "Novel three-phase asymmetrical cascaded multilevel voltage source inverter," *IET Power Electron.*, vol. 6, pp. 1696-1706, 2013.

- [15] M. Farhadi Kangarlu and E. Babaei, "Cross-switched multilevel inverter: an innovative topology," *IET Power Electron.*, vol. 6, pp. 642-651, 2013.

- [16] A. Mokhberdoran and A. Ajami, "Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology," *IEEE Trans. Power. Electron.*, vol. 29, pp. 6712-6724, 2014

- [17] M. Hasan, S. Mekhilef, and M. Ahmed, "Three-phase hybrid multilevel inverter with less power electronic components using space vector modulation," *IET Power Electron.*, vol. 7, pp. 1256-1265, 2014.

- [18] A. L. Batschauer, S. A. Mussa, and M. L. Heldwein, "Three-Phase Hybrid Multilevel Inverter Based on Half-Bridge Modules," *IEEE Trans. Ind. Electron.*, vol. 59, pp. 668-678, 2012.

- [19] D. A. Ruiz-Caballero, R. M. Ramos-Astudillo, S. A. Mussa, and M. L. Heldwein, "Symmetrical hybrid multilevel DC–AC converters with reduced number of insulated DC supplies," *IEEE Trans. Ind. Electron.*, vol. 57, pp. 2307-2314, 2010.

- [20] S. Gui-Jia, "Multilevel dc-link inverter," IEEE Trans. Ind. Appl., vol. 41, pp. 848-854, 2005.

- [21] E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," *Energy Conversion* and Management, vol. 50, pp. 2761-2767, 2009.

- [22] G. Waltrich and I. Barbi, "Three-phase cascaded multilevel inverter using power cells with two inverter legs in series," *IEEE Trans. Ind. Electron.*, vol. 57, pp. 2605-2612, 2010.

- [23] M. M. Hasan, M. Ahmed, and S. Mekhilef, "Analyses and simulation of three-phase MLI with high value of resolution per switch employing SVM control scheme," in 2012 IEEE International Conference on Power and Energy (PECon), 2012, pp. 7-12.

- [24] M. M. Hasan, S. Mekhilef, M. Ahmed, and T. MESSIKH, "Three-phase multilevel inverter with high value of resolution per switch employing a space vector modulation control scheme," *Turkish Journal of Electrical Engineering & Computer Sciences*, vol. 24, pp. 1993-2009, 2016.

- [25] S. Vazquez, J. I. Leon, L. G. Franquelo, J. J. Padilla, and J. M. Carrasco, "DC-voltage-ratio control strategy for multilevel cascaded converters fed with a single DC source," *IEEE Transactions on Industrial Electronics*, vol. 56, pp. 2513-2521, 2009.

- [26] Z. Du, L. M. Tolbert, B. Ozpineci, and J. N. Chiasson, "Fundamental frequency switching strategies of a seven-level hybrid cascaded Hbridge multilevel inverter," *IEEE Transactions on Power Electronics*, vol. 24, pp. 25-33, 2009.

- [27] F.-S. Kang, S.-J. Park, S. E. Cho, C.-U. Kim, and T. Ise, "Multilevel PWM inverters suitable for the use of stand-alone photovoltaic power systems," *IEEE Trans. Energy Conver.*, vol. 20, pp. 906-915, 2005

- [28] S. G. Song, F. S. Kang, and S.-J. Park, "Cascaded multilevel inverter employing three-phase transformers and single dc input," *IEEE Trans. Ind. Electron.*, vol. 56, pp. 2005-2014, 2009.

- [29] M. A. Setiawan, A. Abu-Siada, and F. Shahnia, "A New Technique for Simultaneous Load Current Sharing and Voltage Regulation in DC Microgrids," *IEEE Trans. Ind. Inform.*, 2017.

- [30] H. A. B. Siddique and R. W. D. Doncker, "Evaluation of DC Collector-Grid Configurations for Large Photovoltaic Parks," *IEEE Trans. Power Deliv.*, vol. PP, pp. 1-1, 2017.

- [31] V. Fiore, E. Ragonese, and G. Palmisano, "A Fully Integrated Watt-Level Power Transfer System With On-Chip Galvanic Isolation in Silicon Technology," *IEEE Trans. Power. Electron.*, vol. 32, pp. 1984-1995, 2017.

- [32] L. M. Tolbert, P. Fang Zheng, and T. G. Habetler, "Multilevel PWM methods at low modulation indices," *IEEE Trans. Power. Electron.*, vol. 15, pp. 719-725, 2000.

- [33] S. M. Islam, "Teaching Research Nexus An Australian Experience," in 2009 IEEE Power & Energy Society General Meeting, 2009, pp. 1-5.

- [34] F. Husnayain, N. Purnomo, R. Anwar, and I. Garniwa, "Harmonics mitigation for offshore platform using active filter and line reactor methods," in 2014 International Conference on Electrical Engineering and Computer Science (ICEECS), 2014, pp. 331-336.

- [35] I. Committee, "IEEE standard for interconnecting distributed resources with electric power systems," *IEEE Std.* 1547–2003, pp. 1-28.

- [36] A. Mortezaei, M. G. Simões, A. S. Bubshait, T. D. C. Busarello, F. P. Marafão, and A. Al-Durra, "Multifunctional control strategy for asymmetrical cascaded H-bridge inverter in microgrid applications," *IEEE Trans. Ind. Appl.*, vol. 53, pp. 1538-1551, 2017.

- [37] N. Prabaharan and K. Palanisamy, "A comprehensive review on reduced switch multilevel inverter topologies, modulation techniques and applications," *Renewable and Sustainable Energy Reviews*, vol. 76, pp. 1248-1282, 2017.

- [38] Z. Zheng, K. Wang, L. Xu, and Y. Li, "A hybrid cascaded multilevel converter for battery energy management applied in electric vehicles," *IEEE Trans. Power Electron.*, vol. 29, pp. 3537-3546, 2014

- [39] Tortech. (2017, 03/11/2017). Three Phase Isolation power transformers. Available: https://www.tortech.com.au/category/3phase-isolation-power-transformers

- [40] G. S. Perantzakis, F. H. Xepapas, and S. N. Manias, "A novel four-level voltage source inverter—Influence of switching strategies on the distribution of power losses," *IEEE Trans. Power Electron.*, vol. 22, pp. 149-159, 2007.

- [41] L. He and C. Cheng, "A Flying-Capacitor-Clamped Five-Level Inverter Based on Bridge Modular Switched-Capacitor Topology," *IEEE Trans. Ind. Electron.*, vol. 63, pp. 7814-7822, 2016.

- [42] M. R. Islam, G. Youguang, and Z. Jianguo, "A high-frequency link multilevel cascaded medium-voltage converter for direct grid integration of renewable energy systems," *IEEE Trans. Power Electron.*, vol. 29, pp. 4167-4182, 2014.

- [43] S. Inoue and H. Akagi, "A Bidirectional Isolated DC–DC Converter as a Core Circuit of the Next-Generation Medium-Voltage Power Conversion System," *IEEE Trans. Power Electron.*, vol. 22, pp. 535-542, 2007.

- [44] semikron. (20/10/2017). products price and specification.

Available: https://www.semikron.com/products/product-classes/igbt-modules.html

Md Mubashwar Hasan received the B.Eng. Degree in electrical engineering from Chittagong University of Engineering and Technology, Bangladesh and M.Eng. from the University of Malaya, Kuala Lumpur, Malaysia, in 2010 and 2014, respectively. He is currently pursuing Ph.D. degree in the Department of Electrical Engineering, Curtin

University, Perth, WA, Australia.

His research interests include high power converters, efficient renewable power conditioning techniques and compact electric transformer.

**A. Abu-Siada** (M'07–SM'12) received the B.Sc. and M.Sc. degrees from Ain Shams University, Cairo, Egypt, in 1998, and the Ph.D. degree from Curtin University, Perth, WA, Australia, in 2004, all in electrical engineering.

He is currently an Associate Professor in the Department of Electrical and Computer

Engineering, Curtin University. His research interests include Power System Stability, Condition Monitoring, Power Electronics, and Power Quality. Dr. Abu-Siada is the Editor-in-Chief of the International Journal of Electrical and Electronic Engineering and regular Reviewer for various IEEE transactions. He is the Vice Chair of the IEEE Computation Intelligence Society, WA Chapter.

Mohamed S. A. Dahidah (M'02–SM'10) received the Ph.D. degree in electrical engineering from Multimedia University, Malaysia, in 2007. In November 2007, he was appointed an Assistant Professor in the Department of Electrical and Electronic Engineering, The University of Nottingham, Malaysia Campus. He is currently with the

School of Engineering, Newcastle University, Newcastle Upon Tyne, U.K. He has authored or co-authored a number of refereed journal and conference papers. His research interests include modular multilevel converters, SHE-PWM modulation technique for power electronics converters, battery charger for EVs, solid state transformers and renewable energy integration.

Dr. Dahidah is the Deputy Editor-in-Chief for *IET Power Electronics* and has been a Regular Reviewer for both IEEE and IET journals.